- 您现在的位置:买卖IC网 > Sheet目录3888 > PIC18C801T-I/PT (Microchip Technology)IC MCU ROMLESS A/D PWM 80TQFP

2001 Microchip Technology Inc.

Advance Information

DS39541A-page 105

PIC18C601/801

9.2

PORTB, TRISB and LATB

Registers

PORTB is an 8-bit wide, bi-directional port. The corre-

sponding data direction register is TRISB. Setting a

TRISB bit (= 1) will make the corresponding PORTB pin

an input (i.e., put the corresponding output driver in a

Hi-Impedance mode). Clearing a TRISB bit (= 0) will

make the corresponding PORTB pin an output ( i.e.,

put the contents of the output latch on the selected pin).

Read-modify-write operations on the LATB register

read and write the latched output value for PORTB.

EXAMPLE 9-2:

INITIALIZING PORTB

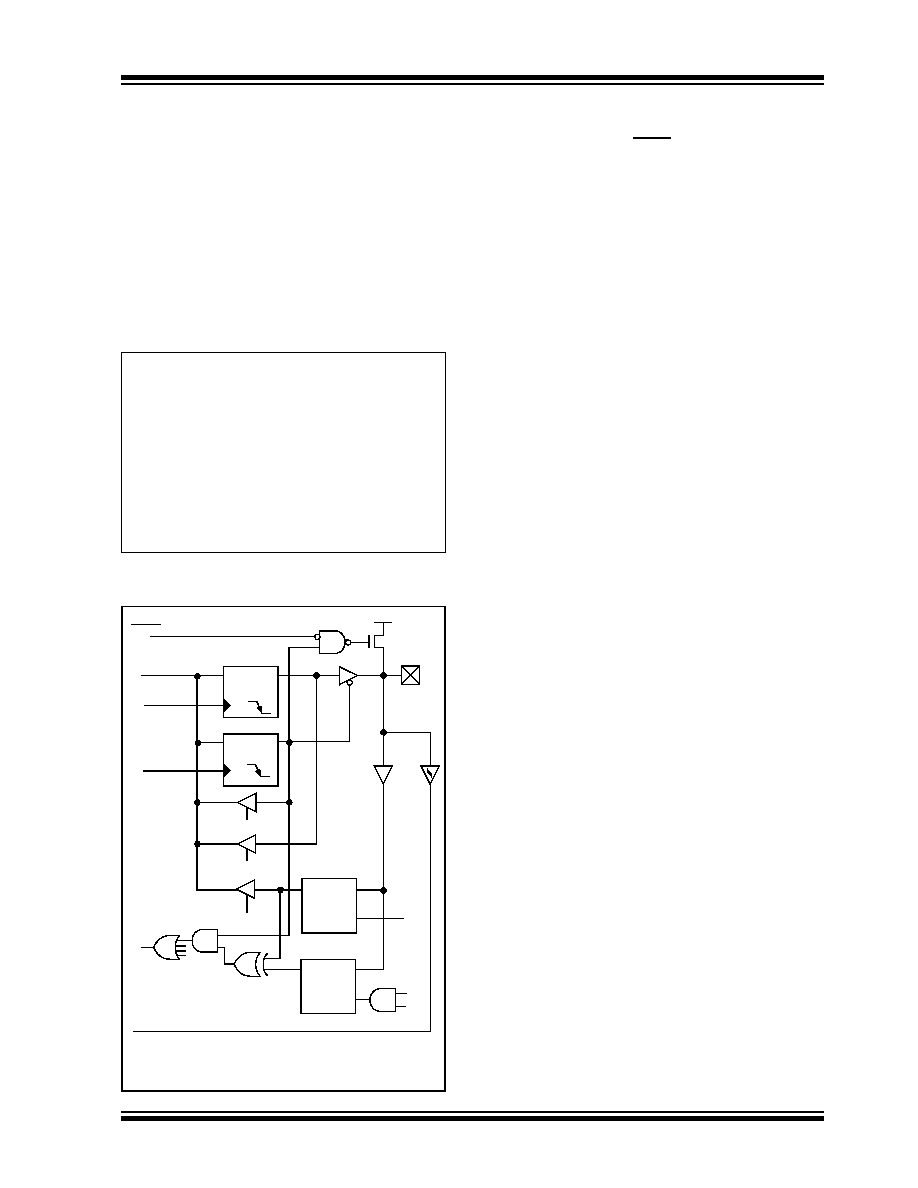

FIGURE 9-3:

RB7:RB4 PINS BLOCK

DIAGRAM

Each of the PORTB pins has a weak internal pull-up. A

single control bit can turn on all the pull-ups. This is per-

formed by clearing bit RBPU (INTCON2 register). The

weak pull-up is automatically turned off when the port

pin is configured as an output. The pull-ups are

disabled on a Power-on Reset.

Pin RB3 is multiplexed with the CCP input/output. The

weak pull-up for RB3 is disabled when the RB3 pin is

configured as CCP pin. By disabling the weak pull-up

when pin is configured as CCP, allows the remaining

weak pull-up devices of PORTB to be used while the

CCP is being used.

Four of PORTB’s pins, RB7:RB4, have an interrupt-on-

change feature. Only pins configured as inputs can

cause this interrupt to occur (i.e., any RB7:RB4 pin

configured as an output is excluded from the interrupt-

on-change comparison). The input pins (of RB7:RB4)

are compared with the old value latched on the last

read of PORTB. The “mismatch” outputs of RB7:RB4

are OR’d together to generate the RB Port Change

Interrupt with flag bit RBIF (INTCON register).

This interrupt can wake the device from SLEEP. The

user, in the Interrupt Service Routine, can clear the

interrupt in the following manner:

a)

Any read or write of PORTB (except with the

MOVFF

instruction). This will end the mismatch

condition.

b)

Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF.

Reading PORTB will end the mismatch condition and

allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for

wake-up on key depression operation and operations

where PORTB is only used for the interrupt-on-change

feature. Polling of PORTB is not recommended while

using the interrupt-on-change feature.

CLRF

PORTB

; Initialize PORTB by

; clearing output

; data latches

CLRF

LATB

; Alternate method

; to clear output

; data latches

MOVLW

0CFh

; Value used to

; initialize data

; direction

MOVWF

TRISB

; Set RB3:RB0 as inputs

; RB5:RB4 as outputs

; RB7:RB6 as inputs

Data Latch

From other

RBPU(2)

P

VDD

I/O pin(1)

Q

D

CK

Q

D

CK

QD

EN

QD

EN

Data Bus

WR LATB

WR TRISB

Set RBIF

TRIS Latch

RD TRISB

RD PORTB

RB7:RB4 pins

Weak

Pull-up

RD PORTB

Latch

TTL

Input

Buffer

ST

Buffer

RBx/INTx

Q3

Q1

RD LATB

or

WR PORTB

Note 1: I/O pins have diode protection to VDD and VSS.

2: To enable weak pull-ups, set the appropriate TRIS bit(s)

and clear the RBPU bit (INTCON2 register).

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

22-15-3073

CONN FFC/FPC 7POS .100 RT ANG

22-02-3073

CONN FFC/FPC VERTICAL 7POS .100

PIC18LC801T-I/PT

IC MCU ROMLESS A/D PWM 80TQFP

22-15-3253

CONN FFC/FPC 25POS .100 RT ANG

PIC16C621AT-40/SS

IC MCU OTP 1KX14 COMP 20SSOP

22-02-3253

CONN FFC/FPC VERTICAL 25POS .100

22-15-3243

CONN FFC/FPC 24POS .100 RT ANG

PIC16CE624T-30/SO

IC MCU OTP 1KX14 EE COMP 18SOIC

相关代理商/技术参数

PIC18C858-E/L

功能描述:8位微控制器 -MCU 32KB 1536 RAM 68I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18C858-E/PT

功能描述:8位微控制器 -MCU 32KB 1536 RAM 68I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18C858EPT

制造商:MICRO CHIP 功能描述:New

PIC18C858-I/L

功能描述:8位微控制器 -MCU 32KB 1536 RAM 68I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18C858-I/PT

功能描述:8位微控制器 -MCU 32KB 1536 RAM 68I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18C858T-E/L

功能描述:8位微控制器 -MCU 40MHz 16K OTP RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18C858T-E/PT

功能描述:8位微控制器 -MCU 32KB 1536 RAM 68I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18C858T-I/L

功能描述:8位微控制器 -MCU 40MHz 16K OTP RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT